Take a closer look.

Deep dives into production hardware systems—from concept to silicon.

Custom CNN inference accelerator achieving 10× speedup over ARM Cortex-A9 baseline. Implements a systolic array MAC engine with INT8 quantization and AXI4-Stream DMA for zero-copy data transfer.

48-hour hackathon project: 50 MSPS digital oscilloscope with real-time FFT display. Built on QNX Neutrino RTOS with deterministic sub-10µs interrupt latency and custom DMA ring-buffer architecture.

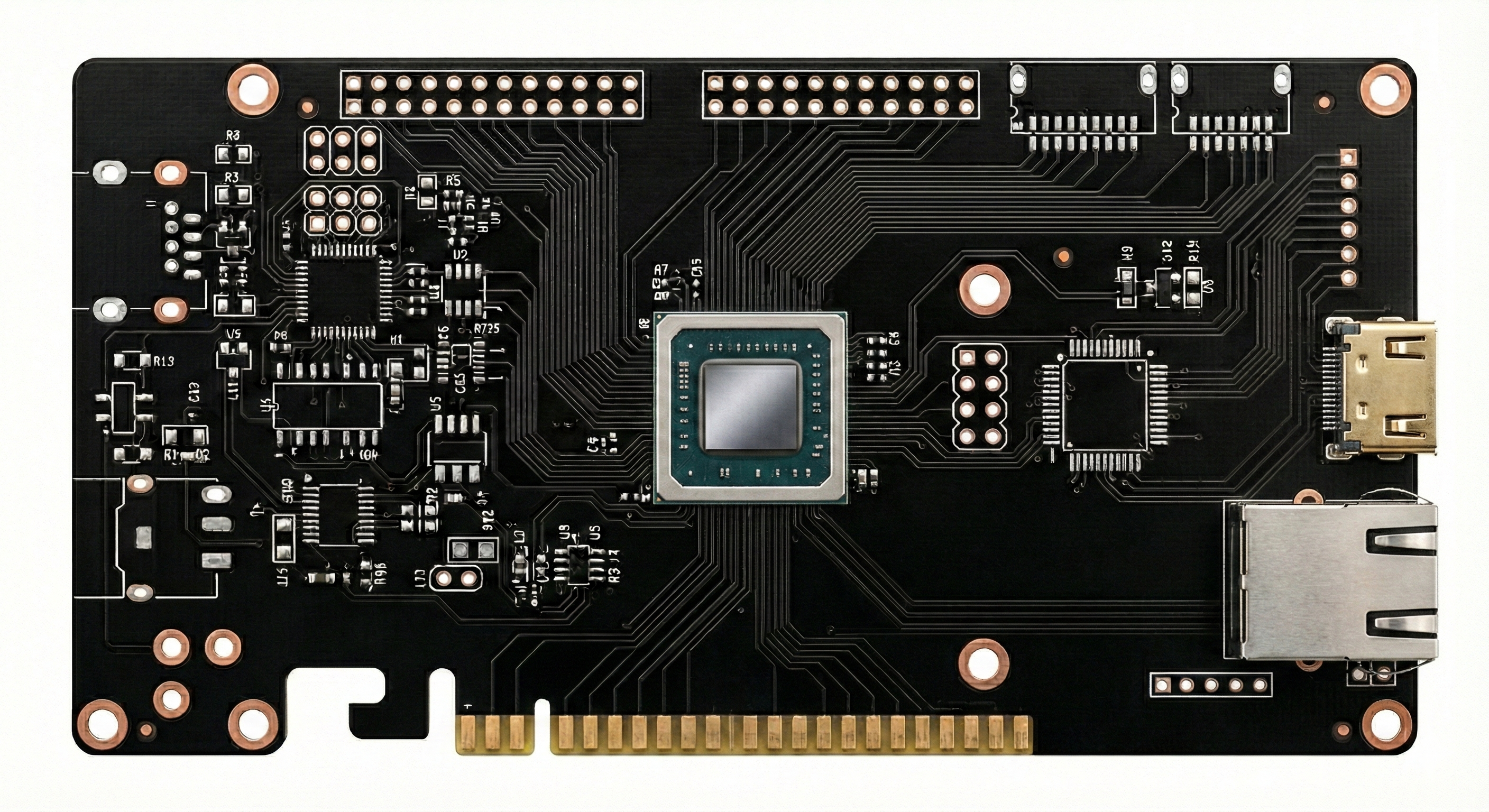

High-bandwidth DMA engine achieving 6.8 GB/s sustained throughput on PCIe 3.0 x8. Features scatter-gather descriptor chains, MSI-X interrupt coalescing, and credit-based flow control for zero packet loss.

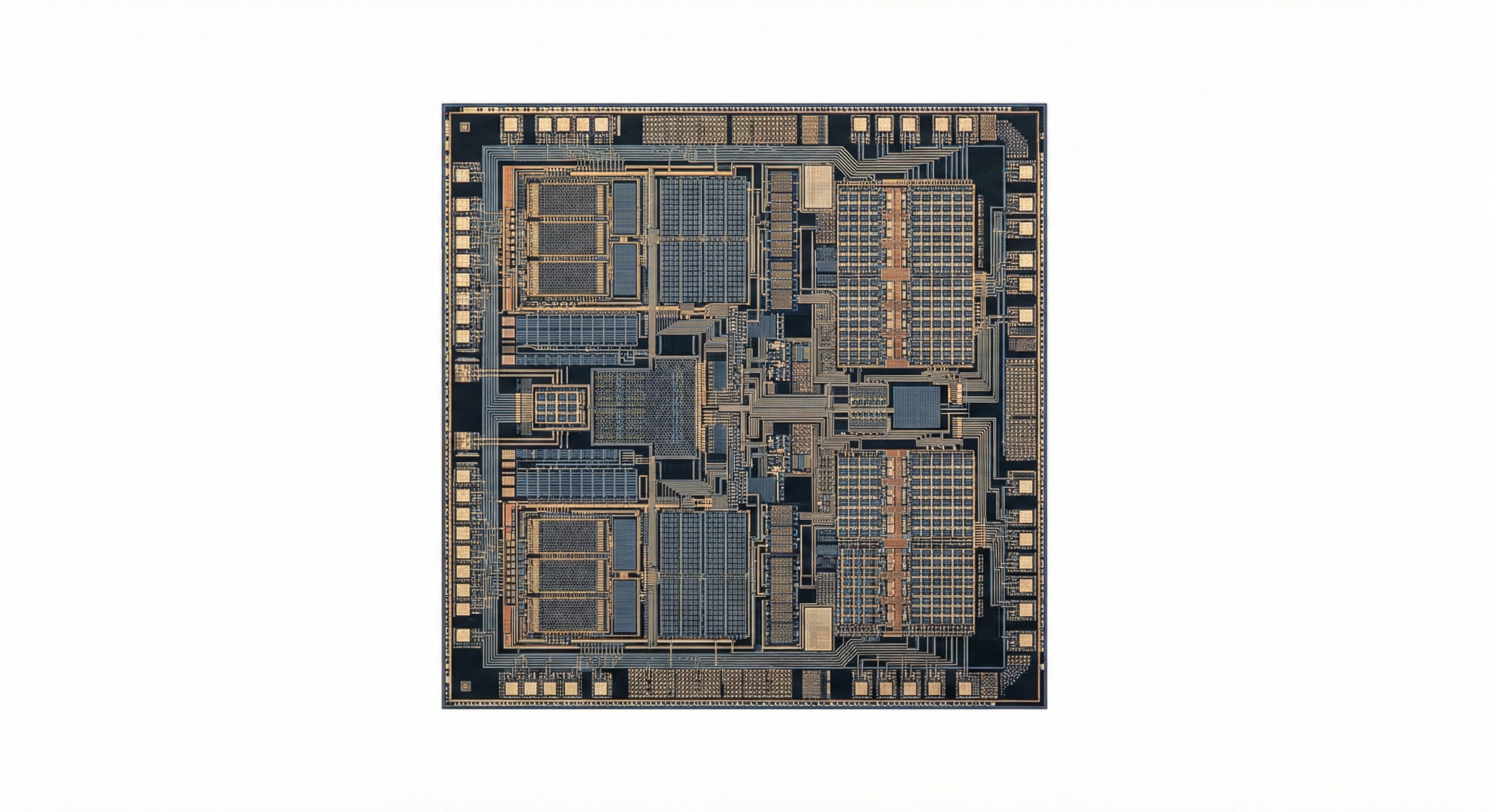

5-stage pipelined RISC-V core with 1.2 DMIPS/MHz and full M-extension support. Includes 2-bit saturating branch predictor, 4KB I-cache, and synthesizes to 220 MHz on 28nm TSMC at 0.85V nominal.